**ULV7266 CMOS IC**

# **ULTRA LOW POWER CMOS OPERATIONAL AMPLIFIERS**

#### DESCRIPTION

The UTC ULV7266 is ultra low supply current, rail-to-rail input and output CMOS operational amplifiers.

The UTC **ULV7266** have an wide operating temperature range. They have a wide input common mode voltage range and output voltage swing, and take the minimum operating supply voltage down to 1.8V. The maximum recommended supply voltage is 5.5V. These features are suitable for portable equipment and sensor amplifiers.

#### **FEATURES**

- \* Low Operating Supply Voltage: 1.8V(MIN)

- \* Ultra Low Supply Current:0.9µA (Typ.)

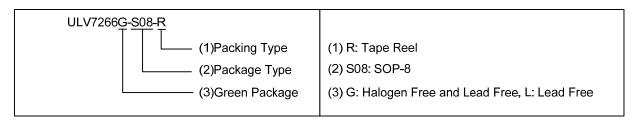

#### ORDERING INFORMATION

| Ordering       | Number         | Dookona | Packing   |  |

|----------------|----------------|---------|-----------|--|

| Lead Free      | Halogen Free   | Package |           |  |

| ULV7266L-S08-R | ULV7266G-S08-R | SOP-8   | Tape Reel |  |

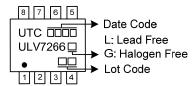

## **MARKING**

www.unisonic.com.tw 1 of 5

## **■ PIN CONFIGURATION**

# **■ PIN DESCRIPTION**

| PIN NO. | PIN NAME        | DESCRIPTION                   |  |  |

|---------|-----------------|-------------------------------|--|--|

| 1       | OUT1            | Output (op amp1)              |  |  |

| 2       | IN1-            | Inverting Input (op amp1)     |  |  |

| 3       | IN1+            | Non-inverting Input (op amp1) |  |  |

| 4       | V <sub>SS</sub> | Negative Power Supply         |  |  |

| 5       | IN2+            | Non-inverting Input (op amp2) |  |  |

| 6       | IN2-            | Inverting Input (op amp2)     |  |  |

| 7       | OUT2            | Output (op amp2)              |  |  |

| 8       | $V_{DD}$        | Positive Power Supply         |  |  |

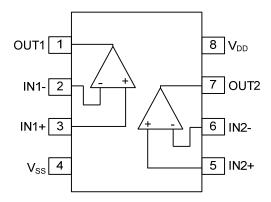

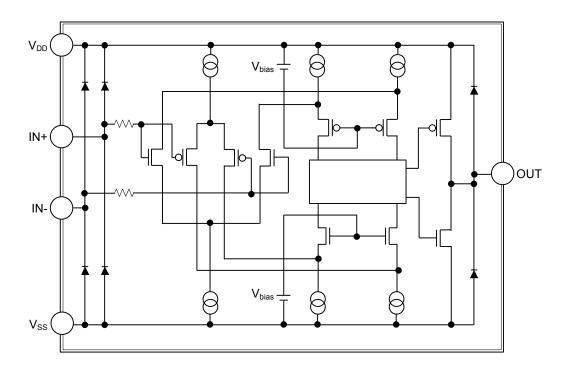

## ■ BLOCK DIAGRAM

# ■ ABSOLUTE MAXIMUM RATING

| PARAMETER                       | SYMBOL              | RATINGS                        | UNIT |

|---------------------------------|---------------------|--------------------------------|------|

| Supply Voltage                  | $V_{DD}$ - $V_{SS}$ | +7                             | V    |

| Differential Input Voltage      | $V_{ID}$            | $V_{DD}$ - $V_{SS}$            | V    |

| Input Common-mode Voltage Range | $V_{ICM}$           | $(V_{SS}-0.3)$ to $V_{DD}+0.3$ | V    |

| Input Current                   | I                   | ±10                            | mA   |

| Operating Supply Voltage        | $V_{OPR}$           | +1.8 ~ +5.5                    | V    |

| Power Dissipation               | $P_{D}$             | 0.55                           | W    |

| Junction Temperature            | $T_J$               | +125                           | °C   |

| Operating Temperature           | T <sub>OPR</sub>    | -40 ~ +85                      | °C   |

| Storage Temperature             | T <sub>STG</sub>    | -55 ~ +125                     | °C   |

Note: Absolute maximum ratings are those values beyond which the device could be permanently damaged. Absolute maximum ratings are stress ratings only and functional device operation is not implied.

# ■ **ELECTRICAL CHARACTERISTICS** (V<sub>DD</sub>=+3V, V<sub>SS</sub>=0V, T<sub>A</sub>=25°C, unless otherwise specified)

| PARAMETER                    | SYMBOL              | TEST CONDITIONS                            |             | MIN                  | TYP | MAX                  | UNIT |

|------------------------------|---------------------|--------------------------------------------|-------------|----------------------|-----|----------------------|------|

| Quiescent Current            | lα                  | R <sub>L</sub> =∞, All<br>Op-Amps          | 25°C        |                      | 0.9 | 1.7                  |      |

|                              |                     | AV=0dB,<br>IN+=1.5V                        | -40°C~+85°C |                      | 2.1 |                      | μA   |

| Power Supply Rejection Ratio | PSRR                |                                            |             | 60                   | 85  |                      | dB   |

| Input Offset Voltage         | Vos                 | V <sub>DD</sub> =1.8V~5.5V                 |             |                      |     | 8.5                  | mV   |

| Input Bias Current           | lΒ                  |                                            |             |                      | 5   |                      | pΑ   |

| Input Offset Current         | los                 |                                            |             |                      | 5   |                      | pΑ   |

| Common-Mode Voltage Range    | $V_{CM}$            | $V_{SS}$ to $V_{DD}$                       |             | 0                    |     | 3                    | V    |

| Common-mode Rejection Ratio  | CMRR                |                                            |             | 45                   | 65  |                      | dB   |

| Large Signal Voltage Gain    | $A_V$               | R <sub>L</sub> =10kΩ                       |             | 60                   | 90  |                      | dB   |

| Output Voltage High          | $V_{OH}$            | $R_L=10k\Omega$                            |             | V <sub>DD</sub> -0.1 |     |                      | V    |

| Output Voltage Low           | $V_{OL}$            | $R_L=10k\Omega$                            |             |                      |     | V <sub>SS</sub> +0.1 | V    |

| Output Source Current        | I <sub>SOURCE</sub> | OUT=V <sub>DD</sub> -0.4V                  |             | 1                    | 2.2 |                      | mΑ   |

| Output Sink Current          | I <sub>SINK</sub>   | OUT=V <sub>SS</sub> +0.4V                  |             | 1                    | 3.2 |                      | mΑ   |

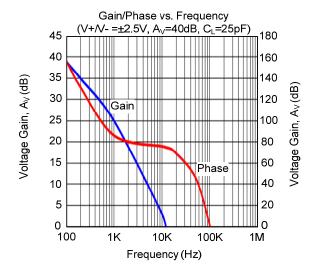

| Slew Rate                    | SR                  | C <sub>L</sub> =25pF                       |             |                      | 3.5 |                      | V/ms |

| Gain-Bandwidth Product       | GBW                 | C <sub>L</sub> =25pF, A <sub>V</sub> =40dB |             |                      | 12  |                      | kHz  |

| Phase Margin                 | θ                   | $C_L$ =25pF, $A_V$ =40dB                   |             |                      | 60  |                      | deg  |

| Channel Separation           | CS                  | A <sub>V</sub> =40dB, OUT=1Vrms            |             |                      | 80  |                      | dB   |

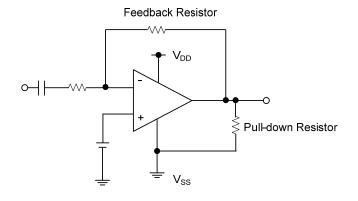

# **■ TYPICAL APPLICATION CIRCUIT**

To Suppress the Crosover Distortion

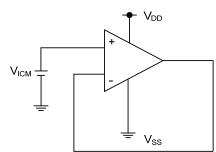

Example of Application Circuit for Unused Op-amp

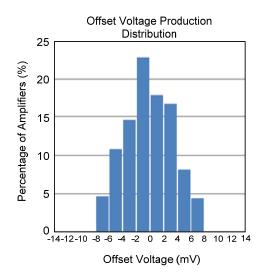

#### ■ TYPICAL CHARACTERISTICS

UTC assumes no responsibility for equipment failures that result from using products at values that exceed, even momentarily, rated values (such as maximum ratings, operating condition ranges, or other parameters) listed in products specifications of any and all UTC products described or contained herein. UTC products are not designed for use in life support appliances, devices or systems where malfunction of these products can be reasonably expected to result in personal injury. Reproduction in whole or in part is prohibited without the prior written consent of the copyright owner. UTC reserves the right to make changes to information published in this document, including without limitation specifications and product descriptions, at any time and without notice. This document supersedes and replaces all information supplied prior to the publication hereof.