# UNISONIC TECHNOLOGIES CO., LTD

# L8603

### LINEAR INTEGRATED CIRCUIT

# 6 STAGE FET LNA BIAS CONTROLLER

#### DESCRIPTION

The UTC L8603 is an advanced GaAs and HEMT FETs bias controller. It is designed to operate from minimal supply rails and intended primarily for satellite Low Noise Blocks (LNBs).

The UTC L8603 provides drain voltage and current control for up to 6 external grounded source FETs with the addition of one capacitor and a resistor.

The UTC L8603 is generating the regulated negative rail required for FET gate biasing whilst operating from a single supply of 2.1V to 5.5V. The -2V negative bias can also be used to supply other external circuits.

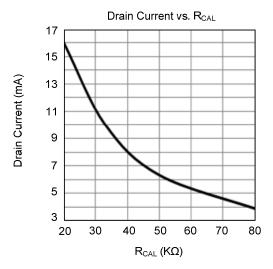

Setting drain currents on the UTC L8603 only requires one resistor which controls the drain current of the first stage FETS (D1 and D4). The drain current is set internally to 10mA for the remaining 4 FETs for the second and third stages. This allows the operating current of input FETs to be adjusted to minimize noise, whilst the following FET stages are fixed to minimize the number of external components used.

#### **FEATURES**

- \* Provides Bias for up to 6 GaAs and HEMT FETs

- 2 x Amplifier FET Drain Current Programmable (4mA to15mA)

- 4 x Amplifier FET Drain Current Internally Fixed to 10mA

- \* Operating Range of 2.1V to 5.5V

- \* Ultra-low Operating Current of 1.1mA

- \* Dynamic FET Protection

- \* Amplifier FET Drain Voltages set at 2.0V,

- \* Regulated Negative Rail Generator Requires only 1 External Capacitor

- \* Low external Component Count

- \* Expended Temperature Range of -40°C to +105°C

#### ORDERING INFORMATION

| Ordering Number   |                   | Doolsono    | Do akin n |  |

|-------------------|-------------------|-------------|-----------|--|

| Lead Free         | Halogen Free      | Package     | Packing   |  |

| L8603L-Q16-3030-R | L8603G-Q16-3030-R | QFN-16(3×3) | Tape Reel |  |

www.unisonic.com.tw 1 of 7

#### ■ MARKING

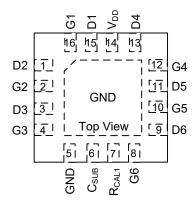

#### **■ PIN CONFIGURATION**

#### **■ PIN DESCRIPTION**

| PIN NO. | PIN NAME          | DESCRIPTION                                  |  |  |

|---------|-------------------|----------------------------------------------|--|--|

| 1       | D2                | Drain GaAs FET 2                             |  |  |

| 2       | G2                | Gate GaAs FET 2                              |  |  |

| 3       | D3                | Drain GaAs FET 3                             |  |  |

| 4       | G3                | Gate GaAs FET 3                              |  |  |

| 5       | GND               | Ground                                       |  |  |

| 6       | C <sub>SUB</sub>  | Negative rail reservoir capacitor            |  |  |

| 7       | R <sub>CAL1</sub> | Drain current setting for D1 and D4          |  |  |

| 8       | G6                | Gate GaAs FET 6                              |  |  |

| 9       | D6                | Drain GaAs FET 6                             |  |  |

| 10      | G5                | Gate GaAs FET 5                              |  |  |

| 11      | D5                | Drain GaAs FET 5                             |  |  |

| 12      | G4                | Gate GaAs FET 4                              |  |  |

| 13      | D4                | Drain GaAs FET 4                             |  |  |

| 14      | $V_{DD}$          | Supply voltage                               |  |  |

| 15      | D1                | Drain GaAs FET 1                             |  |  |

| 16      | G1                | Gate GaAs FET 1                              |  |  |

| Pad     | GND               | Must be connected to Ground or No Connection |  |  |

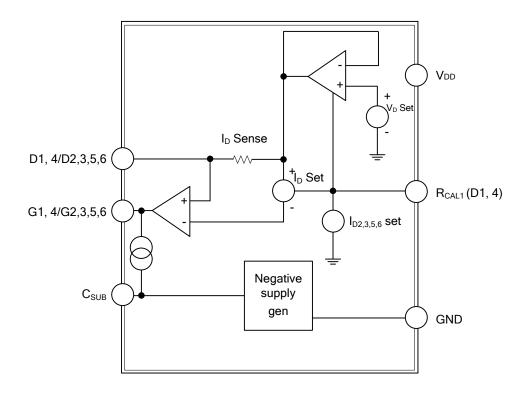

# ■ BLOCK DIAGRAM

#### **■ ABSOLUTE MAXIMUM RATING**

| PARAMETER                 | SYMBOL              | RATINGS    | UNIT |

|---------------------------|---------------------|------------|------|

| Supply Voltage            | $V_{DD}$            | -0.6 ~ +6  | V    |

| Supply Current            | I <sub>DD</sub> 100 |            | mA   |

| Power Dissipation         | $P_{D}$             | 650        | mW   |

| Junction Temperature      | TJ                  | +135       | °C   |

| Storage Temperature Range | T <sub>STG</sub>    | -40 ~ +150 | °C   |

Note: Absolute maximum ratings are those values beyond which the device could be permanently damaged. Absolute maximum ratings are stress ratings only and functional device operation is not implied.

#### ■ RECOMMENDED OPERATING CONDITIONS (Note 5)

| PARAMETER                   | SYMBOL         | RATINGS    | UNIT |

|-----------------------------|----------------|------------|------|

| Operating Voltage Range     | $V_{DD}$       | 2.1 ~ 5.5  | V    |

| Operating Temperature Range | T <sub>A</sub> | -40 ~ +105 | °C   |

## ■ ELECTRICAL CHARACTERISTICS (T<sub>A</sub>=25°C, V<sub>DD</sub> =2.3V, I<sub>D1</sub> to I<sub>D6</sub> set to 10mA)

| PARAMETER                               | SYMBOL         | TEST CONDITIONS                      | MIN  | TYP  | MAX  | UNIT |

|-----------------------------------------|----------------|--------------------------------------|------|------|------|------|

| Supply Current                          | $I_{DD}$       | I <sub>D1-6</sub> =0                 |      | 1.1  | 2.5  | mA   |

|                                         | $I_{DD(L)}$    | I <sub>D1-6</sub> =10mA              |      |      | 65   | mA   |

| Substrate Voltage (Note 2)              | $V_{CSUB}$     | I <sub>CSUB</sub> =0                 | -2.5 | -2.0 | -1.5 | V    |

|                                         | $V_{CSUB(L)}$  | I <sub>CSUB</sub> =-20μA             |      |      | -1.5 | V    |

| Gate Characteristics                    |                |                                      |      |      |      |      |

| Gate (G1 to G6)                         |                |                                      |      |      |      |      |

| Current Range                           | lg             |                                      | -50  |      | 60   | μΑ   |

| Voltage Low                             | $V_{G(L)}$     | $I_D$ =12mA, $I_G$ =-10 $\mu$ A      | -2.5 | -2.0 | -1.5 | V    |

| Voltage High                            | $V_{G(H)}$     | $I_D=8mA$ , $I_G=0$                  | 0    | 0.7  | 1.0  | V    |

| Drain Characteristics                   |                |                                      |      |      |      |      |

| Drain (D1 to D6)                        |                |                                      |      |      |      |      |

| Current Range                           | $I_{D}$        | D1 and D4                            | 4    |      | 15   | mA   |

|                                         | $I_{DD}$       | D2, D3, D5, D6 Internally Fixed      | 10   |      | mA   |      |

| Current Operating (Note 1)              | $I_{D(OP)}$    | Standard Application Circuit 8       |      | 10   | 12   | mA   |

| Voltage Operating (Note 4)              | $V_{D(OP)}$    | I <sub>D</sub> =10mA                 | 1.8  | 2.0  | 2.2  | V    |

| delta V <sub>D</sub> vs V <sub>DD</sub> | $dV_D/dV_{DD}$ | $V_{DD} = 2.3V \sim 5.5V$ 0.15       |      | %/V  |      |      |

| delta I <sub>D</sub> vs V <sub>DD</sub> | $dI_D/dV_{DD}$ | V <sub>DD</sub> = 2.3V~ 5.5V         |      | 1.5  |      | %/V  |

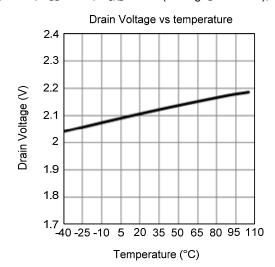

| delta V <sub>D</sub> vs T <sub>A</sub>  | $dV_D/dT_A$    | $T_A = -40^{\circ}C^{+105^{\circ}C}$ |      | 150  |      | ppm  |

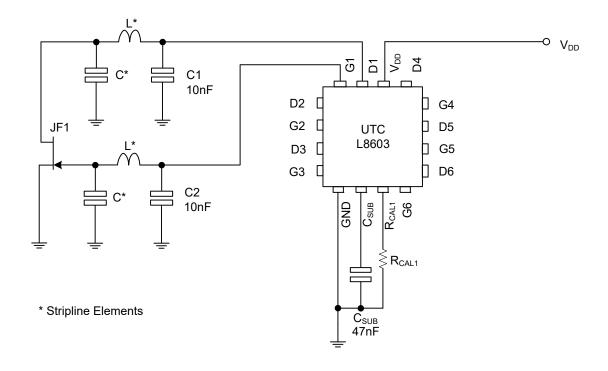

Notes: 1. Characteristics are measured using up to two external reference resistors, RCAL

- 2. The negative bias voltages are generated on-chip using an internal oscillator. An external 47nF capacitor is required for this purpose.

- 3. Noise voltage measurements are made with FETs and gate and drain capacitors of value 10nF in place. Noise voltages are not measured in production.

- 4. The maximum operating drain voltage is equal to  $V_{DD}$  or  $V_{D(OP)}$  max whichever is lower.

- 5. ESD sensitive, handling precautions are recommended.

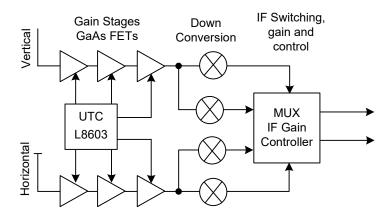

#### ■ TWIN LNB SYSTEM DIAGRAM

#### ■ DEVICE DESCRIPTION

The UTC **L8603** is designed to meet the bias requirements of GaAs and HEMT FETs commonly used in satellite receiver LNBs with a minimum of external components whilst operating from a minimal voltage supply and using minimal current.

The UTC **L8603** has six FET bias stages. To optimize the system for noise and gain the drain current for two of the six stages can be programmed over the range of 4mA to 15mA. Programming the drain current of FETS D1 and D4 is achieved by a resistor connected to the R<sub>CAL1</sub> pin. The Drain current of the remaining four FETS D2, D3, D5 and D6 are internally set to 10mA.

Drain voltages of amplifier stages are set at 2.0V and are current limited to approximately current set by their associated R<sub>CAL</sub> resistors.

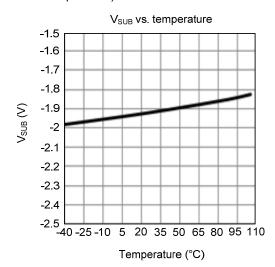

Depletion mode FETs require a negative voltage bias supply when operated in grounded source circuits. The UTC **L8603** includes an integrated switched capacitor DC-DC converter generating a regulated output of -2V to allow single supply operation. The UTC **L8603** has been designed to be used with supply rails of 2.1V to 5.5V and the  $V_{DD}$  range has been extended to 5.5V to allow for 10% supply variation.

It is possible to use less than the full complement of FET bias controls, unused drain and gate connections can be left open circuit without affecting operation of the remaining bias circuits.

To protect the external FETs the circuits have been designed to ensure that, under any conditions including power up/down transients, the gate drive from the bias circuits cannot exceed -2.5V. Additionally each stage has its own individual current limiter. Furthermore if the negative rail experiences a fault condition, such as overload or short circuit, the drain supply to the FETs will be limited, avoiding excessive current flow.

Device operating temperature is -40°C to +105°C to suit a wide range of environmental conditions.

## **■ TYPICAL APPLICATION CIRCUIT**

#### **■ TYPICAL CHARACTERISTICS**

$(T_A=25^{\circ}C, V_{DD}=2.3V, R_{CAL}=33k\Omega \text{ (setting } I_D \text{ to } 10\text{mA}), \text{ unless otherwise specified.)}$

UTC assumes no responsibility for equipment failures that result from using products at values that exceed, even momentarily, rated values (such as maximum ratings, operating condition ranges, or other parameters) listed in products specifications of any and all UTC products described or contained herein. UTC products are not designed for use in life support appliances, devices or systems where malfunction of these products can be reasonably expected to result in personal injury. Reproduction in whole or in part is prohibited without the prior written consent of the copyright owner. UTC reserves the right to make changes to information published in this document, including without limitation specifications and product descriptions, at any time and without notice. This document supersedes and replaces all information supplied prior to the publication hereof.