UPSS3880 Preliminary CMOS IC

# THREE-RAIL SIMPLE POWER SEQUENCER

#### DESCRIPTION

The UTC **UPSS3880** simple power supply sequencer offers the easiest method to control power up sequencing and power down sequencing of multiple Independent voltage rails. By staggering the startup sequence, it is possible to avoid latch conditions or large in-rush currents that can affect the reliability of the system.

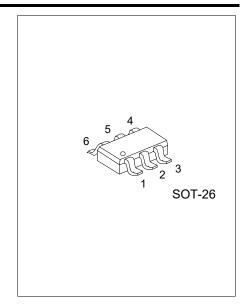

Available in a 6-pin SOT-26 package, the Simple Sequencer contains a precision enable pin and three open-drain output flags. The open-drain output flags permit that they can be pulled up to distinct voltage supplies separate from the sequencer  $V_{\text{DD}}$  (so long as they do not exceed the recommended maximum voltage of 0.3V greater than  $V_{\text{DD}}$ ), so as to interface with ICs requiring a range of different enable signals.

When the UTC **UPSS3880** is enabled, the three output flags will sequentially release, after individual time delays, thus permitting the connected power supplies to start up. The output flags will follow a reverse sequence during power down to avoid latch conditions.

#### **■ FEATURES**

- \* Qualified for Automotive Applications

- \* Simple Solution for Sequencing 3 Voltage Rails from a Single Input Signal

- \* Power-Up and Power-Down Control

- \* Low Quiescent Current of 25µA

- \* Input Voltage Range of 3.3V to 5.5V

- \* Standard Timing Options Available

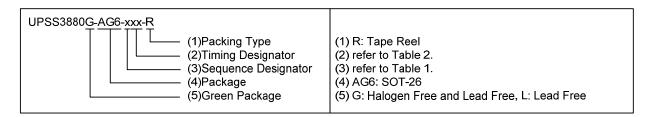

#### ORDERING INFORMATION

| Ordering Number     |                     | Doolsono | Dealing   |  |

|---------------------|---------------------|----------|-----------|--|

| Lead Free           | Halogen Free        | Package  | Packing   |  |

| UPSS3880L-AG6-xxx-R | UPSS3880G-AG6-xxx-R | SOT-26   | Tape Reel |  |

<u>www.unisonic.com.tw</u> 1 of 7

# ■ MARKING

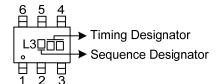

# **■ PIN CONFIGURATION**

# **■ PIN DESCRIPTION**

| PIN NO. | PIN NAME        | DESCRIPTION         |

|---------|-----------------|---------------------|

| 1       | V <sub>CC</sub> | Input supply        |

| 2       | GND             | Ground              |

| 3       | EN              | Enable pin.         |

| 4       | FLAG3           | Open-drain output 3 |

| 5       | FLAG2           | Open-drain output 2 |

| 6       | FLAG1           | Open-drain output 1 |

**Table 1. Sequence Designator Table**

| SEQUENCE NUMBER | FLAG (   | ORDER      |

|-----------------|----------|------------|

|                 | POWER UP | POWER DOWN |

| 1               | 1-2-3    | 3 - 2 - 1  |

**Table 2. Timing Designator Table**

| TIMING<br>DESIGNATOR | t <sub>d1</sub> | t <sub>d2</sub> | t <sub>d3</sub> | t <sub>d4</sub> | t <sub>d5</sub> | t <sub>d6</sub> |

|----------------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|

| AB                   | 30ms            | 30ms            | 30ms            | 30ms            | 30ms            | 30ms            |

| AC                   | 60ms            | 60ms            | 60ms            | 60ms            | 60ms            | 60ms            |

| AD                   | 120ms           | 120ms           | 120ms           | 120ms           | 120ms           | 120ms           |

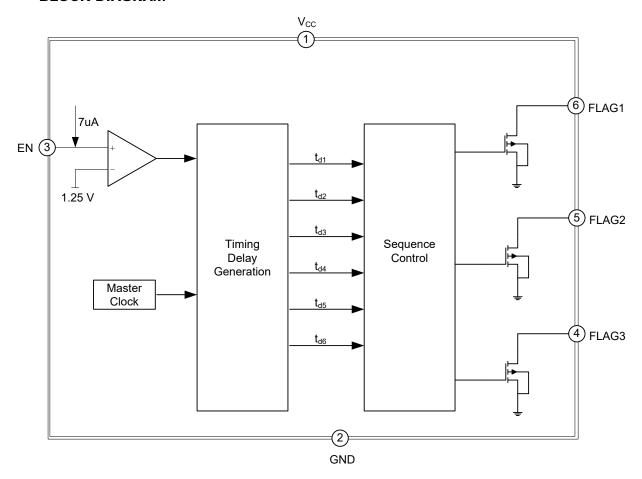

# ■ BLOCK DIAGRAM

### ■ ABSOLUTE MAXIMUM RATING (T<sub>A</sub>=25°C, unless otherwise specified)

| PARAMETER               | SYMBOL           | RATINGS    | UNIT |

|-------------------------|------------------|------------|------|

| Supply Current          | V <sub>CC</sub>  | 6.0        | V    |

| EN, FLAG1, FLAG2, FLAG3 |                  | 6.0        | V    |

| Junction Temperature    | TJ               | +150       | °C   |

| Storage Temperature     | T <sub>STG</sub> | -65 ~ +150 | °C   |

Note: Absolute maximum ratings are those values beyond which the device could be permanently damaged. Absolute maximum ratings are stress ratings only and functional device operation is not implied.

### ■ **RECOMMENDED OPERATING CONDITIONS** (T<sub>A</sub>=25°C, unless otherwise specified)

| PARAMETER               | SYMBOL                 | RATINGS              | UNIT |

|-------------------------|------------------------|----------------------|------|

| Supply Voltage          | V <sub>CC</sub> to GND | 3.3 ~ 5.5            | V    |

| EN, FLAG1, FLAG2, FLAG3 |                        | V <sub>CC</sub> +0.3 | V    |

# ■ THERMAL DATA

| PARAMETER                    | SYMBOL        | RATINGS | UNIT |

|------------------------------|---------------|---------|------|

| Junction to Ambient (Note 3) | $\theta_{JA}$ | 240     | °C/W |

### ■ ELECTRICAL CHARACTERISTICS (V<sub>DD</sub>=3.3V, T<sub>A</sub>=25°C, unless otherwise specified)

| PARAMETER                  | SYMBOL                                  | TEST CONDITIONS          | MIN | TYP  | MAX | UNIT |

|----------------------------|-----------------------------------------|--------------------------|-----|------|-----|------|

| Supply Current (Quiescent) | ΙQ                                      |                          |     | 25   | 80  | μΑ   |

| OPEN-DRAIN FLAGS           |                                         |                          |     |      |     |      |

| FLAGX Leakage Current      | $I_{FLAG}$                              | VFLAGX=3.3V              |     | 0.1  | 1   | μΑ   |

| FLAGX Output Voltage Low   | $V_{OL}$                                | IFLAGX=1.2mA             |     |      | 0.4 | V    |

| POWER-UP SEQUENCE          |                                         |                          | ā.  | -    | ā.  | _    |

| Timer Delay 1 Accuracy     | t <sub>d1</sub>                         | All Other Timing Options | -15 |      | 15  | %    |

| Timer Delay 2 Accuracy     | t <sub>d2</sub>                         | All Other Timing Options | -15 |      | 15  | %    |

| Timer Delay 3 Accuracy     | t <sub>d3</sub>                         | All Other Timing Options | -15 |      | 15  | %    |

| POWER-DOWN SEQUENCE        |                                         |                          | ā.  | -    | ā.  | _    |

| Timer Delay 4 Accuracy     | t <sub>d4</sub>                         | All Other Timing Options | -15 |      | 15  | %    |

| Timer Delay 5 Accuracy     | t <sub>d5</sub>                         | All Other Timing Options | -15 |      | 15  | %    |

| Timer Delay 6 Accuracy     | t <sub>d6</sub>                         | All Other Timing Options | -15 |      | 15  | %    |

| TIMING DELAY ERROR         |                                         |                          |     |      |     |      |

| Ratio of Timing Delays     | $(t_{d(x)}-400\mu s)$<br>/ $t_{d(x+1)}$ | For x=1 or 4             | 95  |      | 105 | %    |

|                            | $t_{d(x)} / t_{d(x+1)}$                 | For x=2 or 5             | 95  |      | 105 | %    |

| ENABLE PIN                 |                                         |                          | -   |      | -   |      |

| EN Pin Threshold           | $V_{EN}$                                |                          | 1.0 | 1.25 | 1.4 | V    |

| EN Pin Pull Up Current     | I <sub>EN</sub>                         | V <sub>EN</sub> =0V      |     | 7    |     | μA   |

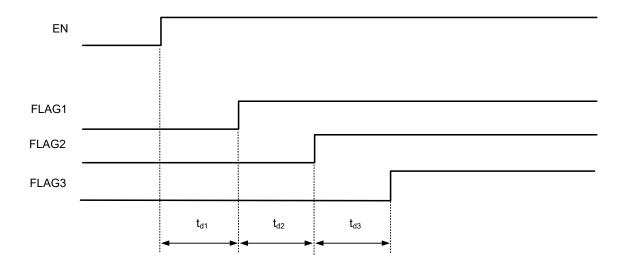

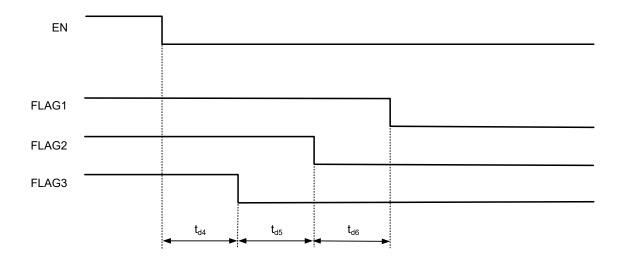

# ■ TIMING DIAGRAMS

# **Power-Up Sequence**

**Power-Down Sequence**

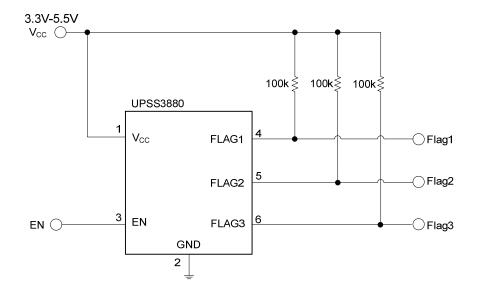

#### APPLICATION INFORMATION

The Simple Power Supply Sequencer contains three open-drain output flags which need to be pulled up for properoperation.100- $k\Omega$  resistors can be used as pull up resistors.

The Simple Power Supply Sequencer is used to implement a power-up and power-down sequence of three power supplies.

UTC **UPSS3880** has a power-up sequence (1 -2-3) and power-down sequence (3 -2-1).

#### ■ DETAILED DESCRIPTION

#### Overview

The UTC **UPSS3880** simple power supply sequencer provides a simple solution for sequencing multiple rails in a controlled manner. Six independent timers are integrated to control the timing sequence (power up and power down) of three open-drain output flags. These flags permit connection to either a shutdown or enable pin of linear regulators and switchers to control the operation of the power supplies. This allows design of a complete power system without concern for large inrush currents or latch-up conditions that can occur.

The timing sequence of the device is controlled entirely by the enable (EN) pin. Upon power up, all the flags are held low until this precision enable is pulled high. When the EN pin is asserted, the power-up sequence starts. An internal counter delays the first flag (FLAG1) from rising until a fixed time period has expired. When the first flag is released, another timer will begin to delay the release of the second lag (FLAG2). This process repeats until all three flags have sequentially been released.

The power-down sequence is the same as power-up sequence, but in reverse. When the EN pin is deasserted a timer will begin that delays the third flag (FLAG3) from pulling low. The second and first flag will then follow in a sequential manner after their appropriate delays. The three timers that are used to control the power-down scheme can also be individually programmed and are completely independent of the power-up timers.

#### **Enable Control**

The timing sequence of the UTC **UPSS3880** is controlled by the assertion of the enable signal. The enable pin is designed with an internal comparator, referenced to a bandgap voltage (1.25V), to provide a precision threshold. This allows a delayed timing to be externally set using a capacitor or to start the sequencing based on a certain event, such as a line voltage reaching 90% of nominal. For an additional delayed sequence from the rail powering  $V_{CC}$ , simply attach a capacitor to the EN pin.

#### **■ TYPICAL APPLICATION CIRCUIT**

UTC assumes no responsibility for equipment failures that result from using products at values that exceed, even momentarily, rated values (such as maximum ratings, operating condition ranges, or other parameters) listed in products specifications of any and all UTC products described or contained herein. UTC products are not designed for use in life support appliances, devices or systems where malfunction of these products can be reasonably expected to result in personal injury. Reproduction in whole or in part is prohibited without the prior written consent of the copyright owner. UTC reserves the right to make changes to information published in this document, including without limitation specifications and product descriptions, at any time and without notice. This document supersedes and replaces all information supplied prior to the publication hereof.