U8C3060

**Preliminary**

# LINEAR INTEGRATED CIRCUIT

# 8 CHANNEL SERIAL INTERFACE LOW-SIDE DRIVER

#### DESCRIPTION

The **U8C3060** provides an 8-channel low side driver with overcurrent protection and open/shorted load detection. It has built-in diodes to clamp turn-off transients generated by inductive loads, and can be used to drive unipolar stepper motors, DC motors, relays, solenoids, or other loads.

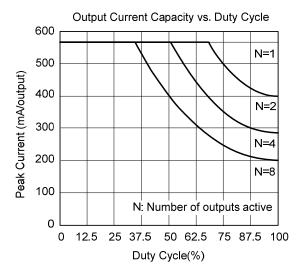

**U8C3060** can supply up to 200mA × 8 channel continuous output current. The current driving capability increased with lower PWM duty cycle. A single channel can deliver up to 560 mA continuous output current.

A serial interface is provided to control the **U8C3060** output drivers, configure internal setting register and read the fault status of each channel. Multiple **U8C3060** devices can be daisy-chained together to use a single serial interface. Energizing-time and holding-PWM-Duty cycles are configurable through serial interface as well. These functions allow for cooler running than traditional always-on solutions.

Internal shutdown functions are provided for overcurrent protection, short-circuit protection, under voltage lockout, and overtemperature. **U8C3060** can diagnosis an open load condition. Fault information for each channel can be read out through serial interface and indicated by an external fault pin.

# ■ FEATURES

- \* 8 Channel Protected Low-side Driver Eight NMOS FETs with Overcurrent Protection Integrated Inductive Catch Diodes Serial Interface Open/Short Load Detection Configurable 100% Output Timing

- \* Continuous Current Driving Capability

560 mA (Single Channel)

200 mA (8 Channels)

Support Parallel Configuration

Configurable PWM Duty Cycle

- \* 8 V to 38 V Supply Voltage Range

- \* Input Digital Noise Filter for Noise Immunity

- \* Internal Data Read Back Capability for Reliable Control

- Protection and Diagnostic Features

Overcurrent Protection (OCP)

Open Load Detection (OL)

Over Temperature Shutdown (OTS)

Under Voltage Lockout (UVLO)

Individual Channel Status Report

Fault Condition Alarm

# ORDERING INFORMATION

| Ordering N     | Number         | Doolsono | Dealing   |

|----------------|----------------|----------|-----------|

| Lead Free      | Halogen Free   | Package  | Packing   |

| U8C3060L-P16-R | U8C3060G-P16-R | TSSOP-16 | Tape Reel |

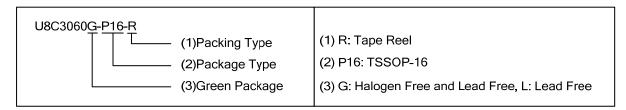

# MARKING

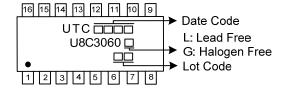

# ■ PIN CONFIGURATION

# ■ PIN DESCRIPTION

| PIN NO. | PIN NAME                                                                              | DESCRIPTION                                                                             |  |  |  |  |

|---------|---------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|--|--|--|--|

| 1       | V <sub>M</sub>                                                                        | Motor power supply                                                                      |  |  |  |  |

| 2       | DIN                                                                                   | Serial data input;                                                                      |  |  |  |  |

| 2       | DIN                                                                                   | Serial data input from controller. Internal pulldown.                                   |  |  |  |  |

|         |                                                                                       | Serial clock input;                                                                     |  |  |  |  |

| 3       | CLK                                                                                   | Rising edge clocks data into part for write operations. Falling edge clocks data out of |  |  |  |  |

|         |                                                                                       | part for read operations. Internal pulldown.                                            |  |  |  |  |

| 4       | LATCH                                                                                 | Serial latch signal;                                                                    |  |  |  |  |

| 4       | LATON                                                                                 | Refer to serial communication waveforms. Internal pulldown.                             |  |  |  |  |

| 5       | GND                                                                                   | Device ground                                                                           |  |  |  |  |

| 6       | DOUT                                                                                  | Serial data output;                                                                     |  |  |  |  |

| 0       | DOOT                                                                                  | Serial data output to controller. Open-drain output with internal pullup.               |  |  |  |  |

| 7       | nFAULT Logic low when in fault condition. Open-drain output requires external pullup. |                                                                                         |  |  |  |  |

| ,       | III AGET                                                                              | Faults: OCP, OL, OTS, UVLO                                                              |  |  |  |  |

| 8       | ENABLE                                                                                | Logic high to enable outputs, logic low to disable outputs. Internal logic and          |  |  |  |  |

|         | LIVIOLE                                                                               | registers can be read and written to when ENABLE is logic low. Internal pulldown.       |  |  |  |  |

| 9       | OUT8                                                                                  |                                                                                         |  |  |  |  |

| 10      | OUT7                                                                                  |                                                                                         |  |  |  |  |

| 11      | OUT6                                                                                  |                                                                                         |  |  |  |  |

| 12      | OUT5                                                                                  | NEET output driver. Connect external lead between this nin and \/                       |  |  |  |  |

| 13      | OUT4                                                                                  | NFET output driver. Connect external load between this pin and V <sub>M</sub>           |  |  |  |  |

| 14      | OUT3                                                                                  |                                                                                         |  |  |  |  |

| 15      | OUT2                                                                                  |                                                                                         |  |  |  |  |

| 16      | OUT1                                                                                  |                                                                                         |  |  |  |  |

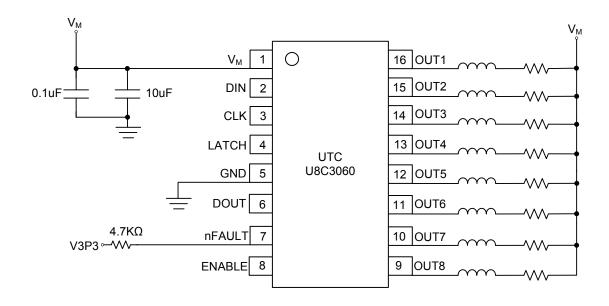

Table 1. External Components

| COMPONENT             | PIN1                                  | PIN2   | RECOMMENDED                                           |

|-----------------------|---------------------------------------|--------|-------------------------------------------------------|

|                       | \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ | CND    | 0.1 μF ceramic capacitor rated for V <sub>M</sub>     |

| C <sub>(VM)</sub>     | V <sub>M</sub>                        | GND    | 10 μF electrolytic capacitor rated for V <sub>M</sub> |

| R <sub>(nFAULT)</sub> | V3P3 (Note)                           | nFAULT | > 4.7 kΩ                                              |

Note: V3P3 is not a pin on the U8C3060, but a V3P3 supply voltage pullup is required for open-drain output nFAULT.

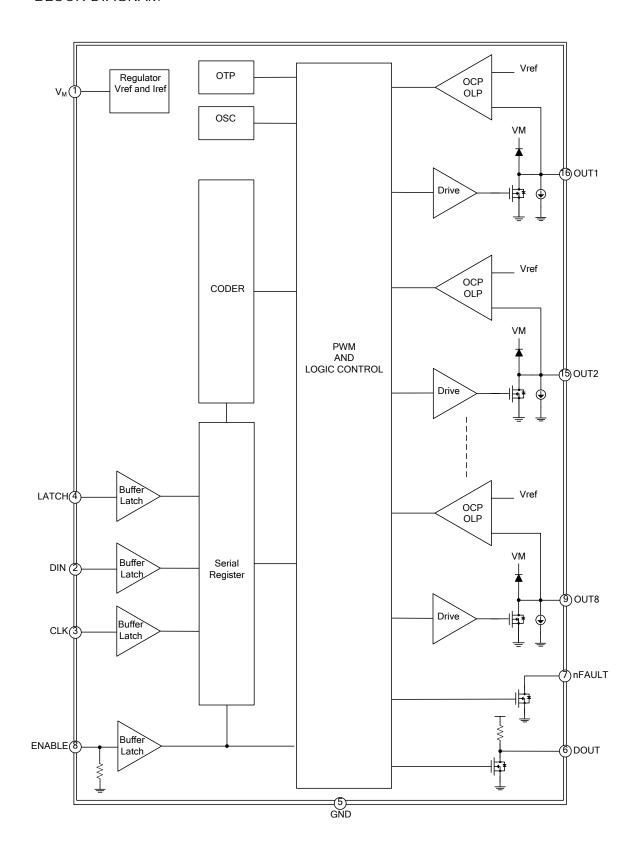

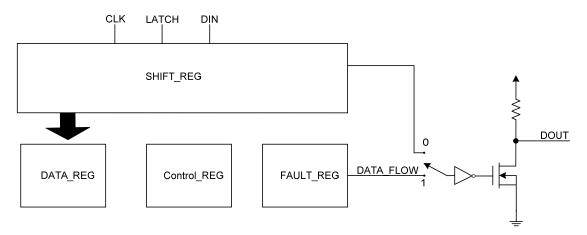

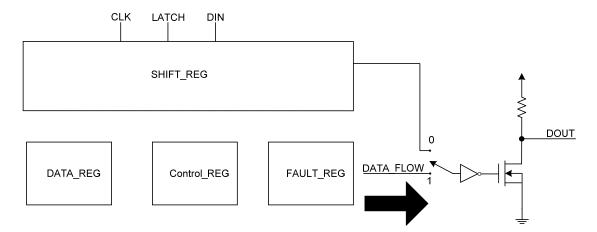

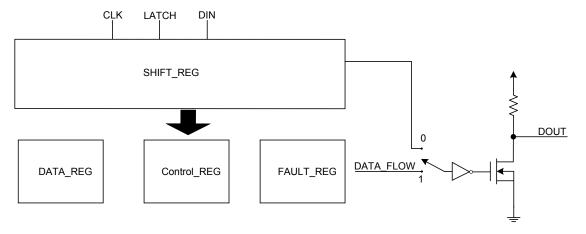

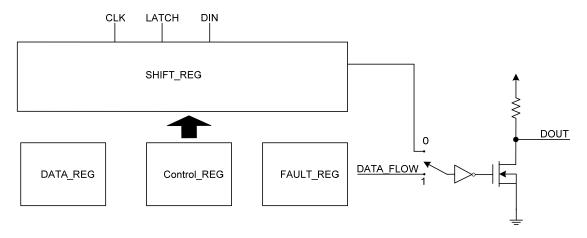

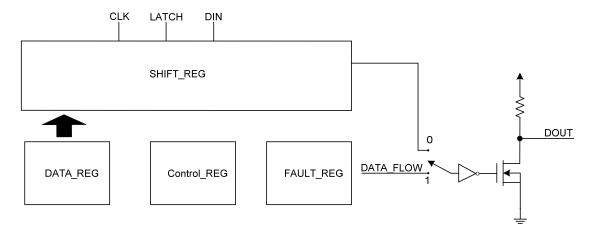

# ■ BLOCK DIAGRAM

# ABSOLUTE MAXIMUM RATING

| PARAMETER                                   | SYMBOL           | RATINGS            | UNIT |

|---------------------------------------------|------------------|--------------------|------|

| Power supply voltage range                  | $V_{M}$          | -0.3 ~ 40          | V    |

|                                             | DIN, LATCH,      |                    |      |

| Digital input pin current range             | CLK.             | 0 ~ 20             | mA   |

|                                             | ENABLE           |                    |      |

| Digital autout pip valtage repre            | nFAULT、          | 0.57               |      |

| Digital output pin voltage range            | DOUT             | -0.5 ~ 7           | V    |

| Digital autout pin august                   | nFAULT、          | 0.57               |      |

| Digital output pin current                  | DOUT             | -0.5 ~ 7           | V    |

| Output voltage range                        | OUT <sub>X</sub> | -0.3 ~ 40          | V    |

| Output current range                        | OUT <sub>X</sub> | Internally limited | Α    |

| Operating vitual junction temperature range | TJ               | -40 ~ +150         | °C   |

| Storage temperature range                   | T <sub>STG</sub> | -60 ~ +150         | °C   |

Note: 1.Absolute maximum ratings are those values beyond which the device could be permanently damaged.

Absolute maximum ratings are stress ratings only and functional device operation is not implied.

- 2. All voltage values are with respect to network ground terminal.

- 3. Power dissipation and thermal limits must be observed.

# ■ RECOMMENDED OPERATING CONDITIONS

Over operating free-air temperature range (unless otherwise noted)

| PARAMETER                           | SYMBOL           | MIN | TYP | MAX | UNIT |

|-------------------------------------|------------------|-----|-----|-----|------|

| Motor power supply voltage range    | $V_{M}$          | 8   |     | 38  | V    |

| Low-side driver current capability  | l <sub>out</sub> |     |     | 560 | mA   |

| Operating ambient temperature range | T <sub>A</sub>   | -40 |     | 85  | °C   |

# ■ THERMAL DATA

| PARAMETER           | SYMBOL        | RATINGS | UNIT |

|---------------------|---------------|---------|------|

| Junction to Ambient | $\theta_{JA}$ | 103     | °C/W |

# ■ ELECTRICAL CHARACTERISTICS

(T<sub>A</sub> = 25°C, over recommended operating conditions unless otherwise noted.)

| TIA - 20 0, OVER RECOMMENDED       | ting condition      | is diffess offici wise floted.            |     |     |     |      |

|------------------------------------|---------------------|-------------------------------------------|-----|-----|-----|------|

| PARAMETER                          | SYMBOL              | TEST CONDITION                            | MIN | TYP | MAX | UNIT |

| POWER SUPPLIES                     |                     | <del>-</del>                              |     |     |     |      |

| VM operating supply current        | I <sub>(VM)</sub>   | V <sub>M</sub> =24V                       |     | 3   | 4.5 | mA   |

| VM under voltage lockout voltage   | $V_{(UVLO)}$        | V <sub>M</sub> rising                     |     |     | 8.2 | V    |

| LOGIC-LEVEL INPUTS (DIN, ENABL     | E,CLK,LATCI         | H,)                                       |     |     |     |      |

| Input low voltage                  | V <sub>IL</sub>     |                                           | 0   |     | 0.7 | V    |

| Input high voltage                 | V <sub>IH</sub>     |                                           | 1.5 |     | 5.3 | V    |

| Input hysteresis                   | V <sub>HYS</sub>    |                                           | 100 |     |     | mV   |

| Input low current                  | V <sub>IL</sub>     | V <sub>IN</sub> =0                        | -20 |     | 20  | uA   |

| Input high current                 | V <sub>IH</sub>     | V <sub>IN</sub> =3.3V                     |     |     | 100 | uA   |

| Input pulldown resistance          | $R_{PD}$            |                                           |     | 125 |     | kΩ   |

| DOUT,nFAULT OUTPUTS (OPEN-D        | RAIN OUTPU          | ĮTS)                                      |     |     |     |      |

| Output low voltage                 | V <sub>OL</sub>     | I <sub>O</sub> =5mA                       |     |     | 0.5 | V    |

| Output high leakage current        | I <sub>OH</sub>     | V <sub>O</sub> =3.3V,nFAULT               | -1  |     | 1   | uA   |

| Input pullup resistance            | $R_{PU}$            | DOUT only (Pull up to internal 5.7V)      |     | 1.4 |     | kΩ   |

| LOW-SIDE FET DRIVERS               |                     |                                           |     |     |     |      |

| FET on resistance                  | R <sub>DS(ON)</sub> | V <sub>M</sub> =24V,I <sub>O</sub> =150mA |     | 3   |     | Ω    |

| Off-state leakage current          | I <sub>OFF</sub>    | V <sub>M</sub> =24V                       | 0   | 30  |     | uA   |

| HIGH-SIDE FREE-WHEELING DIOD       | ES                  |                                           |     |     |     |      |

| Diode forward voltage              | $V_{F}$             | V <sub>M</sub> =24V,I <sub>O</sub> =150mA |     | 0.9 |     | V    |

| PROTECTION CIRCUITS                |                     |                                           |     |     |     |      |

| Overcurrent protection trip level  | I <sub>OCP</sub>    | Each channel separately monitored         |     | 620 |     | mA   |

| Open load detect pull-down current | I <sub>OL</sub>     | Each channel separately monitored         |     | 30  |     | μA   |

| Open load detect threshold voltage | V <sub>OL</sub>     | Each channel separately monitored         |     | 1.2 |     | ٧    |

| Thermal shutdown temperature       | T <sub>TSD</sub>    | Die temperature                           | 150 | 160 | 180 | °C   |

| Thermal shutdown hysteresis        | T <sub>HYS</sub>    | Die temperature                           |     | 35  |     | °C   |

| PWM CHOPPING FREQUENCY             |                     |                                           |     |     |     |      |

|                                    |                     | Duty cycle is >25%                        |     | 40  |     |      |

| PWM chopping frequency             | F <sub>PWM</sub>    | Duty cycle is 25%                         |     | 20  |     | kHz  |

|                                    |                     | Duty cycle is 12.5%                       |     | 10  |     |      |

# ■ TIMING REQUIREMENTS

| PARMMETER                            | SYMBOL          | TEST CONDITION                             | MIN | TYP | MAX  | UNIT |

|--------------------------------------|-----------------|--------------------------------------------|-----|-----|------|------|

| Rise time                            | $t_R$           | I <sub>O</sub> =150mA,V <sub>M</sub> =24V, | 50  |     | 300  | ns   |

| Fall time                            | t <sub>F</sub>  | resistive load                             | 50  |     | 300  | ns   |

| Overcurrent protection deglitch time | tocp            | V <sub>M</sub> =24V                        | 2.7 | 3.5 | 3.85 | μs   |

| Open load detect deglitch time       | t <sub>OL</sub> | Each channel separately monitored          | 14  | 17  | 20   | μs   |

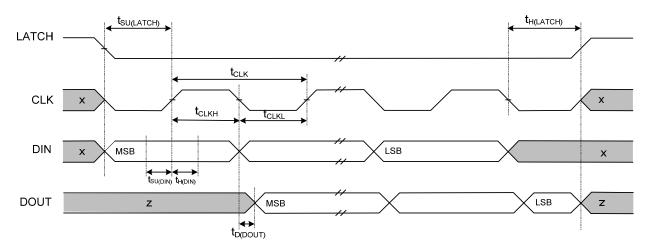

# ■ SERIAL INTERFACE

Table 2. Serial Timing

| NO. | REF DES                 | DESCRIPTION                           | MIN | TYP | MAX | UNIT |

|-----|-------------------------|---------------------------------------|-----|-----|-----|------|

| 1   | t <sub>CLK</sub>        | CLK cycle time                        | 5   |     |     | μs   |

| 2   | t <sub>CLKH</sub>       | CLK high time                         | 2.5 |     |     | μs   |

| 3   | t <sub>CLKL</sub>       | CLK low time                          | 2.5 |     |     | μs   |

| 4   | t <sub>SU(DIN)</sub>    | Setup time, DIN to CLK                | 1   |     |     | μs   |

| 5   | t <sub>H(DIN)</sub>     | Hold time, DIN to CLK                 | 1   |     |     | μs   |

| 6   | t <sub>SU(LATCH)</sub>  | Setup time, LATCH to CLK              | 1   |     |     | μs   |

| 7   | t <sub>H(LATCH)</sub>   | Hold time, LATCH to CLK               | 1   |     |     | μs   |

| 8   | t <sub>OFF(LATCH)</sub> | Inactive time between writes and read | 2   |     |     | μs   |

| 9   | t <sub>D(DOUT)</sub>    | Delay time, CLK to DOUT               |     |     | 1.5 | μs   |

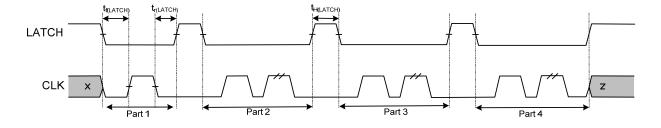

# ■ SPECIAL COMMANDS

Table 3. Special Commands

| NO. | REF DES               | DESCRIPTION            |   | TYP | MAX | UNIT |

|-----|-----------------------|------------------------|---|-----|-----|------|

| 10  | t <sub>f(LATCH)</sub> | LATCH fall to CLK rise | 1 |     |     | μs   |

| 11  | t <sub>r(LATCH)</sub> | CLK fall to LATCH rise | 1 |     |     | μs   |

| 12  | t <sub>H(LATCH)</sub> | LATCH high time        | 2 |     |     | μs   |

## ■ RECOMMENDED OUTPUT CURRENT

Table 4. OUTPUT CURRENT RECOMMENDATION (T<sub>A</sub> = 25°C)

| CONFIGURATION                   | OUTPUT CURRENT CAPACITY |

|---------------------------------|-------------------------|

| 1x output on (100% duty cycle)  | 566mA                   |

| 2x outputs on (100% duty cycle) | 400mA per output        |

| 4x outputs on (100% duty cycle) | 283mA per output        |

| 8x outputs on (100% duty cycle) | 200mA per output        |

Note: **U8C3060** current capability will depend on several system application parameters such as system ambient temperature, maximum case temperature, and overall output duty cycle.

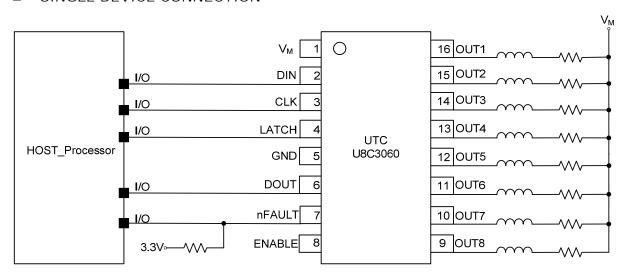

# ■ SINGLE DEVICE CONNECTION

Fig 1. Single Device Connection

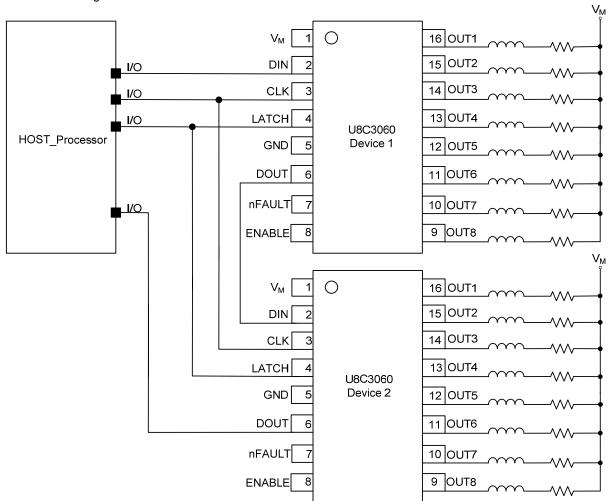

# DAISY-CHAIN CONNECTION

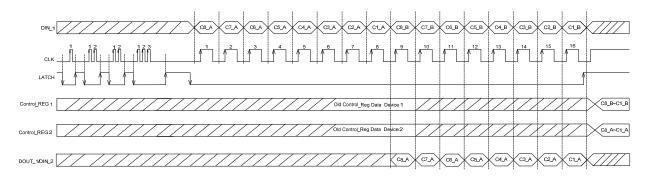

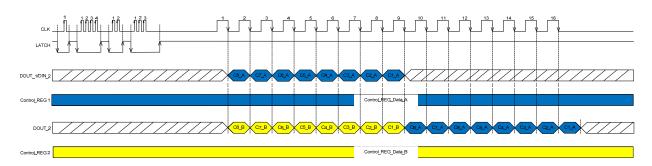

Two or more **U8C3060** devices may be connected together to use a single serial interface. The DOUT pin of the first device in the chain is connected to the DIN pin of the next device. The CLK, LATCH, RESET, and nFAULT pins are connected together.

Fig 2. Daisy-Chain Connection

## ■ REGISTER MAPS

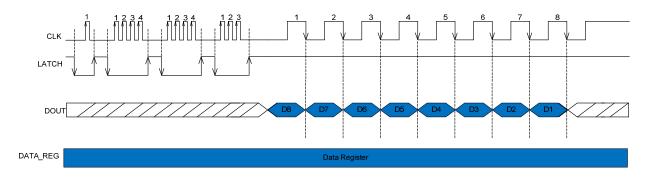

#### **Data Register**

The Data register is used to control the status of each of the eight outputs:

Table 5. Data Register

| D1   | D2   | D3   | D4   | D5   | D6   | D7   | D8   |

|------|------|------|------|------|------|------|------|

| R/W  |

| OUT1 | OUT2 | OUT3 | OUT4 | OUT5 | OUT6 | OUT7 | OUT8 |

LEGEND: R/W=Read/Write;

When any bitis '1', the corresponding output will be active. When any bitis '0', the output will be inactive.

The data register is the default write location for the serial interface. In order to read back data from this register, the Data Register Readout special command is used.

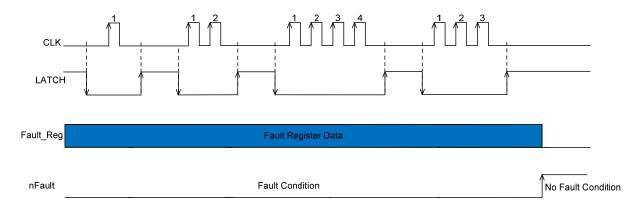

## **Fault Register**

The Fault register can be read to determine if any channel exist fault condition. OCP is an overcurrent fault and OLD is an open load fault.

Table 6. Fault Register

| F1       | F2       | F3       | F4       | F5       | F6       | F7       | F8       |

|----------|----------|----------|----------|----------|----------|----------|----------|

| R/W      |

| OUT1_OL  | OUT2_OL  | OUT3_OL  | OUT4_OL  | OUT5_OL  | OUT6_OL  | OUT7_OL  | OUT8_OL  |

| F9       | F10      | F11      | F12      | F13      | F14      | F15      | F16      |

| R/W      |

| OUT1_OCP | OUT2_OCP | OUT3_OCP | OUT4_OCP | OUT5_OCP | OUT6_OCP | OUT7_OCP | OUT8_OCP |

LEGEND: R/W=Read/Write;

When any fault occurs, nFAULT pin will be driven low and corresponding Fault register bit will be set up as'1'. OCP is a flag indicating overcurrent fault. ODP is a flag indicating open load fault.

Fault bits can be reset by two approaches:

- 1. Special command 'FAUL TRESET' clear all fault bits.

- 2. Setting Data register to ON will clear corresponding OLD bits.

Setting Data register to OFF will clear corresponding OCP bits.

## **Control Register**

The Control register is used to adjust the Energizing Time and PWM Duty Cycle of outputs:

Table 7. Control Register

| C1                      | C2 | C3 | C4  | C5           | C8              |     |  |  |

|-------------------------|----|----|-----|--------------|-----------------|-----|--|--|

| R/W                     |    |    |     |              | R/W             | R/W |  |  |

| Energizing Time control |    |    | PWM | Duty Cycle c | Over All Enable |     |  |  |

LEGEND: R/W=Read/Write;

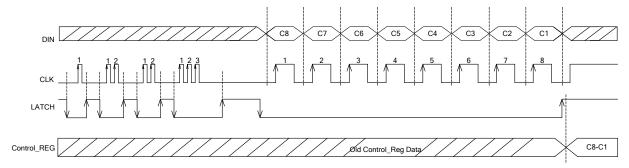

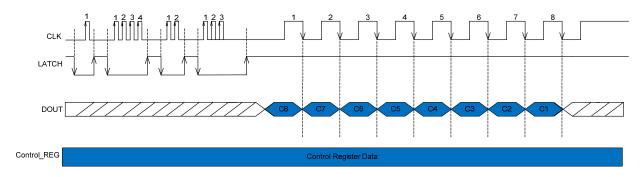

Special command 'WRITE CONTROL REGISTER' is used to program control register.

Special command 'READ CONTROL REGISTER' is used to readback control register content.

#### ■ PROGRAMMING

#### **Serial Control Interface**

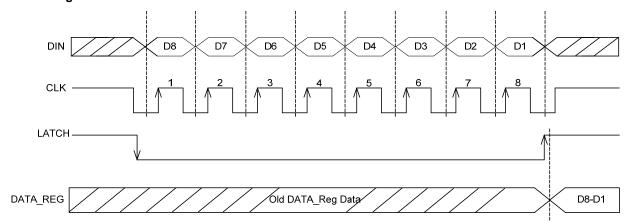

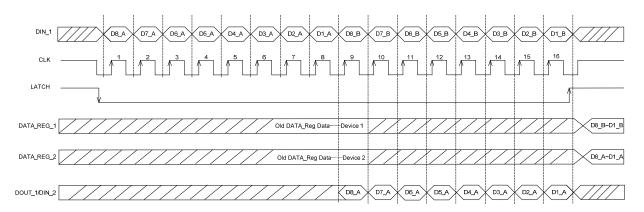

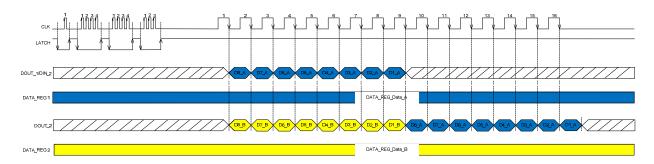

**U8C3060** is using a daisy chain serial interface. Data is latched into the register on the rising edge of the LATCH pin. Data is clocked in on the rising edge of CLK when writing, and data is clocked out on the falling edge of CLK when reading.

# **Data Writing Wave form**

Fig 3. Writing Data Register \_Single Device

Fig 4. Writing Data Register \_Daisy-Chain

Fig 5. Writing Data Register\_Data Flow

# ■ PROGRAMMING (Cont.)

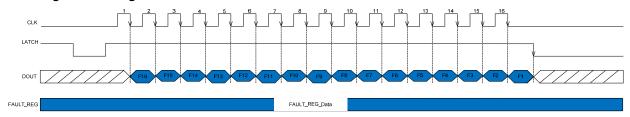

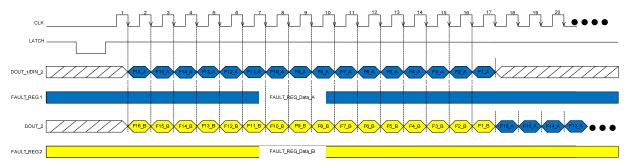

# **Fault Register Reading Waveform**

Fig 6. Reading Fault Register \_Single Device

Fig 7. Reading Fault Register \_Daisy-Chain

Fig 8. Reading Fault Register - Data Flow

# ■ PROGRAMMING (Cont.)

## **Special Command**

Besides output ON/OFF control and fault status reading back, **U8C3060** has special functions to make system more robust or power efficient. These functions will need special command to initiate the device or configure the internal registers.

There are 5 Special Commands:

- 1. Write Control Register command

- 2. Read Control Register command

- 3. Read Data Register command

- 4. Fault Register Reset command

- 5. PWM Start command

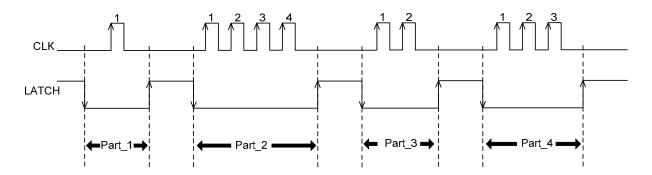

Special waveform pattern on CLK and LATCH pin will issue the special command, as below

Fig 9. Special Command

| Consider a managed     | CLK cycles in each part |       |       |       |  |  |  |

|------------------------|-------------------------|-------|-------|-------|--|--|--|

| Special command        | Part1                   | Part2 | Part3 | Part4 |  |  |  |

| Write Control Register | 1                       | 2     | 2     | 3     |  |  |  |

| Read Control Register  | 1                       | 4     | 2     | 3     |  |  |  |

| Read Data Register     | 1                       | 4     | 4     | 3     |  |  |  |

| Fault Register Reset   | 1                       | 2     | 4     | 3     |  |  |  |

| PWM Start              | 1                       | 6     | 6     | 3     |  |  |  |

PROGRAMMING (Cont.)

## **Special command: Write Control Register**

When Write-Control-Register command is issued, the following serial data will be latched into timing and duty control register.

Fig 10. Writing Control Register \_Single Device

Fig 11. Writing Control Register \_Daisy-Chain

Fig 12. Writing Control Register - Data Flow

# ■ PROGRAMMING (Cont.)

#### **Special command: Read Control Register**

When Read-Control-Register command is issued, control register content will be copied to internal shift register and following CLK will shift this content out from DOUT pin. This provides a mechanism for system to verify the control register is correctly programmed.

Fig 13. Reading Control Register \_Single Device

Fig 14. Reading Control Register \_Daisy-Chain

Fig 15. Read Control Register - Data Flow

PROGRAMMING (Cont.)

## Special command: Read Data Register

When Read-Data-Register command is issued, internal output data register content will be copied to internal shift register and following CLK will shift this content out from DOUT pin. This provides a mechanism for system to verify the output data is correctly programmed. It makes system more robust in noisy system.

Fig 16. Reading Data Register\_Single Device

Fig 17. Reading Control Register\_Daisy-Chain

Fig 18. Reading Data Register\_Data Flow

# PROGRAMMING (Cont.)

## **Special command: Fault Register Reset**

When Fault-Register-Reset command is issued, internal 16bit fault register will be cleared. System can use this method to clear out all fault condition in every chained device at once.

Fig 19. Fault Register Reset

## Special command: PWM Start

When Fault-Register-Reset command is issued, output channel will ignore energizing time and directly enter into PWM mode following the setting in control register.

Fig 20. PWM Start Command

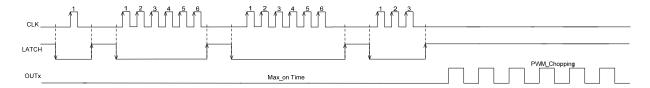

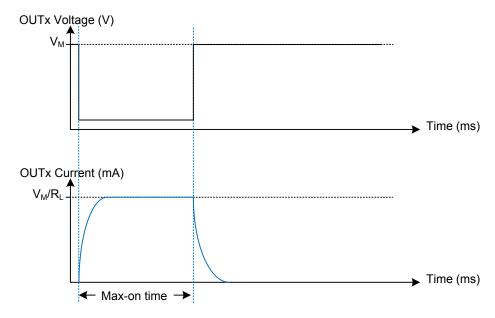

# OUTPUT ENERGIZING AND PWM CONTROL

The device output is defined by two stages: Energizing Phase and PWM Phase.

During the Energizing phase, the channel is turned on with 100% duty cycle for a duration set by Control register bits C4:C1.

In PWM chopping phase, with the PWM Duty Cycle defined by Control register bits C7:C5.

The behavior of each bit in the Control Register is described in Table 8.

Table 8. Control Register Settings

| DESCRIPTION                                                                   |        | Value  | C1 | C2 | C3 | C4 | C5 | C6 | C7 | C8 |

|-------------------------------------------------------------------------------|--------|--------|----|----|----|----|----|----|----|----|

| Outputs always in Energizing mode                                             |        | N/A    | Χ  | Χ  | Χ  | Χ  | Χ  | Χ  | Χ  | 0  |

| No Energizing, starts in PWM chopping                                         |        | 0 ms   | 0  | 0  | 0  | 0  | Χ  | Χ  | Χ  | 1  |

|                                                                               | 3 ms   | 1      | 0  | 0  | 0  | Χ  | Χ  | Χ  | 1  |    |

| Sets the EnergizingTime(100% duty cycle)                                      |        | 5 ms   | 0  | 1  | 0  | 0  | Χ  | Χ  | Χ  | 1  |

|                                                                               |        | 10 ms  | 1  | 1  | 0  | 0  | Χ  | Χ  | Χ  | 1  |

|                                                                               |        | 15 ms  | 0  | 0  | 1  | 0  | Χ  | Χ  | Χ  | 1  |

|                                                                               |        | 20 ms  | 1  | 0  | 1  | 0  | Χ  | Χ  | Χ  | 1  |

|                                                                               |        | 30 ms  | 0  | 1  | 1  | 0  | Χ  | Χ  | Χ  | 1  |

|                                                                               |        | 50 ms  | 1  | 1  | 1  | 0  | Χ  | Χ  | Χ  | 1  |

|                                                                               |        | 80 ms  | 0  | 0  | 0  | 1  | Χ  | Χ  | Χ  | 1  |

| before switching to PWM Phase                                                 |        | 110 ms | 1  | 0  | 0  | 1  | Χ  | Χ  | Χ  | 1  |

|                                                                               |        | 140 ms | 0  | 1  | 0  | 1  | Χ  | Χ  | Χ  | 1  |

|                                                                               |        | 170 ms | 1  | 1  | 0  | 1  | Χ  | Χ  | Χ  | 1  |

|                                                                               |        | 200 ms | 0  | 0  | 1  | 1  | Χ  | Χ  | Χ  | 1  |

|                                                                               |        | 230 ms | 1  | 0  | 1  | 1  | Χ  | Χ  | Χ  | 1  |

|                                                                               |        | 260 ms | 0  | 1  | 1  | 1  | Χ  | Х  | X  | 1  |

|                                                                               | 300 ms | 1      | 1  | 1  | 1  | Χ  | Χ  | Χ  | 1  |    |

| Output is off after Energizing Phase                                          |        | 0 %    | Χ  | Χ  | Х  | Χ  | 0  | 0  | 0  | 1  |

|                                                                               | 10kHz  | 12.5 % | Χ  | Χ  | Х  | Χ  | 1  | 0  | 0  | 1  |

| Sets PWM chopping duty cycle.DC is the Duty cycle that the low-side FETis on. | 20kHz  | 25 %   | Χ  | Χ  | Х  | Χ  | 0  | 1  | 0  | 1  |

|                                                                               | 40kHz  | 37.5 % | Χ  | Χ  | Х  | Χ  | 1  | 1  | 0  | 1  |

|                                                                               |        | 50 %   | Χ  | Χ  | Χ  | Χ  | 0  | 0  | 1  | 1  |

|                                                                               |        | 62.5 % | Χ  | Χ  | Χ  | Χ  | 1  | 0  | 1  | 1  |

|                                                                               |        | 75 %   | Χ  | Χ  | Χ  | Χ  | 0  | 1  | 1  | 1  |

|                                                                               |        | 87.5 % | Χ  | Χ  | Χ  | Χ  | 1  | 1  | 1  | 1  |

OUTPUT ENERGIZING AND PWM CONTROL (Cont.)

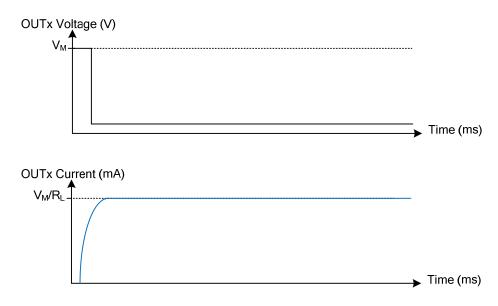

There are five operation cases as described on the following sections. The output is turned on with 100% duty cycle.

Fig 21. Case1: Timer enable bit(C8) is 0(Default value)

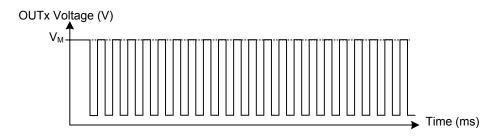

The output is turned on in PWM chopping mode with duty cycle defined by Control register bits C7:C5.

Fig 22. Case2: Timer enable bit (C8) is 1 and Energizing Timing bits (C4:C1) are 0000

# OUTPUT ENERGIZING AND PWM CONTROL (Cont.)

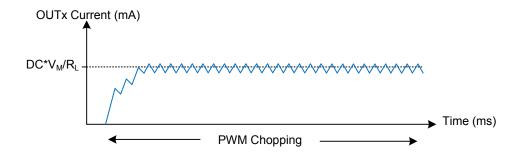

The output is turned on in Energizing mode with 100% duty cycle for a duration set by Control register bits C4:C1. After the timer expires, the output switches to PWM chopping mode with PWM Duty Cycle defined by Control register bits C7:C5.

Fig 23. Case3: Timer enable bit (C8) is 1, Energizing Timing bits (C4:C1) are NOT0000, and PWM Duty bits (C7:C5) are NOT 000

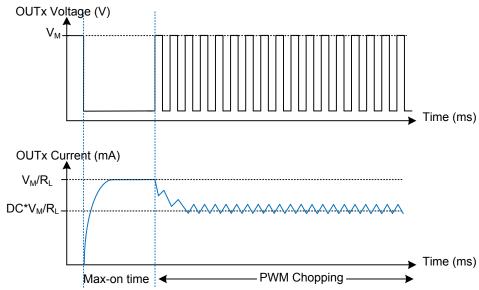

The output is turned on in Energizing mode with 100% duty cycle for aduration set by Control register bits C4:C1.After the timer expires,the output is turned off.

Fig 24. Case4: Timer enable bit (C8) is 1,Energizing Timing bits (C4:C1) are NOT 0000, and PWM Duty bits (C7:C5) are 000

#### APPLICATION AND IMPLEMENTATION

#### **Application Information**

The **U8C3060** is an eight channel low side driver with protection features. The following design is a common application of the **U8C3060**.

#### ■ TYPICAL APPLICATION

Table 9. Design Requirements

| Parameter           | Value             |  |  |  |

|---------------------|-------------------|--|--|--|

| Input voltage range | 8V~38V            |  |  |  |

| Current             | 330mA per channel |  |  |  |

UTC assumes no responsibility for equipment failures that result from using products at values that exceed, even momentarily, rated values (such as maximum ratings, operating condition ranges, or other parameters) listed in products specifications of any and all UTC products described or contained herein. UTC products are not designed for use in life support appliances, devices or systems where malfunction of these products can be reasonably expected to result in personal injury. Reproduction in whole or in part is prohibited without the prior written consent of the copyright owner. UTC reserves the right to make changes to information published in this document, including without limitation specifications and product descriptions, at any time and without notice. This document supersedes and replaces all information supplied prior to the publication hereof.