# UNISONIC TECHNOLOGIES CO., LTD

**UWD706 CMOS IC**

## MICROPROCESSOR UP WATCH DOG TIMER

#### DESCRIPTION

The UTC UWD706 microprocessor supervisory circuit reduces the complexity and number of components required to monitor power-supply and monitor microprocessor activity. It significantly improves system reliability and accuracy compared to separate ICs or discrete components.

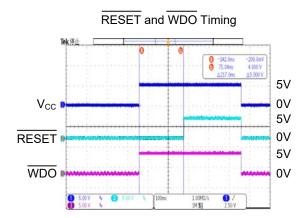

The UTC UWD706 provides power-supply monitoring circuitry that generates a reset output during power-up, power-down and brownout conditions. The reset output remains operational with V<sub>CC</sub> as low as 1V. Independent watchdog monitoring circuitry is also provided. This is activated if the watchdog input has not been toggled within 1.6 seconds.

In addition, there is a 1.25V threshold detector for power-fail warning, low-battery detection, or monitoring an additional power supply. An active-low manual-reset input (MR) is also included.

#### **FEATURES**

- \* Precision supply- Voltage Monitor

- \* Valid RESET remains with V<sub>CC</sub> as low as 1V

- \* 200ms Reset Pulse Width

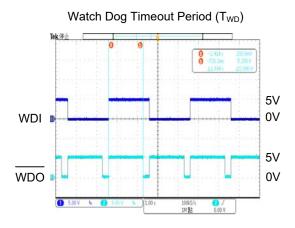

- \* Independent Watchdog Timer (1.6sec) Timeout

- \* Voltage Monitor for Power-Fail or Low-Battery Warning

- \* With Manual reset input

#### ORDERING INFORMATION

| Ordering        | Dookogo         | Dealing |           |  |

|-----------------|-----------------|---------|-----------|--|

| Lead Free       | Halogen Free    | Package | Packing   |  |

| UWD706L-x-S08-R | UWD706G-x-S08-R | SOP-8   | Tape Reel |  |

Note: x: Output Voltage, refer to Marking Information.

www.unisonic.com.tw 1 of 9 UWD706 cmos ic

## MARKING INFORMATION

| PACKAGE | VOLTAGE CODE                                                         | MARKING                                                                               |

|---------|----------------------------------------------------------------------|---------------------------------------------------------------------------------------|

| SOP-8   | A: 2.63V<br>B: 2.93V<br>C: 3.08V<br>D: 4.00V<br>H: 4.40V<br>G: 4.65V | Voltage Code  Voltage Code  UWD706 UWD706 G: L: Lead Free  OG: Halogen Free  Lot Code |

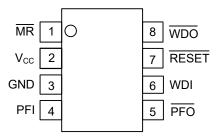

## **■ PIN CONFIGURATION**

## **■** PIN DESCRIPTION

| PIN NO. | PIN NAME | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |

|---------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 1       | MR       | Manual-Reset Input triggers a reset pulse when pulled below 0.8V. This active-low input has an internal $500\mu A$ ( $V_{CC}$ = +5V) pull-up current. It can be driven from a TTL or CMOS logic line as well as shorted to ground with a switch.                                                                                                                                                                                                                                                                                 |  |  |  |

| 2       | $V_{CC}$ | Power Supply Voltage that is monitored.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

| 3       | GND      | 0V Ground Reference for all signals.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |

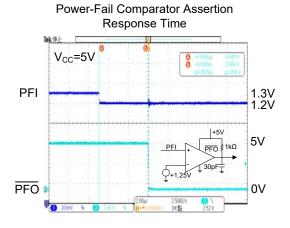

| 4       | PFI      | Power-Fail Voltage Monitor Input. When PFI is less than 1.25V, $\overline{\text{PFO}}$ goes low. Connect PFI to GND or V <sub>CC</sub> when not used.                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |

| 5       | PFO      | Power-Fail Output goes low and sinks current when PFI is less than 1.25V; otherwise PFO stays high.                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

| 6       | WDI      | Watchdog Input. If WDI remains high or low for 1.6sec, the internal watchdog timer runs out and WDO goes low (BLOCK DIAGRAM). Floating WDI or connecting WDI to a high-impedance three-state buffer disables the watchdog feature. The internal watchdog timer clears whenever reset is asserted, WDI is three-stated, or WDI sees a rising or falling edge.                                                                                                                                                                     |  |  |  |

| 7       | RESET    | Active-Low Reset Output pulses low for 200ms when triggered, and stays low whenever $V_{CC}$ is below the reset threshold. It remains low for 200ms after $V_{CC}$ rises above the reset threshold or $\overline{MR}$ goes from low to high. A watchdog timeout will not trigger $\overline{RESET}$ unless $\overline{WDO}$ is connected to $\overline{MR}$ .                                                                                                                                                                    |  |  |  |

| 8       | WDO      | Watchdog Output pulls low when the internal watchdog timer finishes its 1.6sec count and does not go high again until the watchdog is cleared. $\overline{\text{WDO}}$ also goes low during low-line conditions. Whenever $V_{\text{CC}}$ is below the reset threshold, $\overline{\text{WDO}}$ stays low; however, unlike $\overline{\text{RESET}}$ , $\overline{\text{WDO}}$ does not have a minimum pulse width. As soon as $V_{\text{CC}}$ rises above the reset threshold, $\overline{\text{WDO}}$ goes high with no delay. |  |  |  |

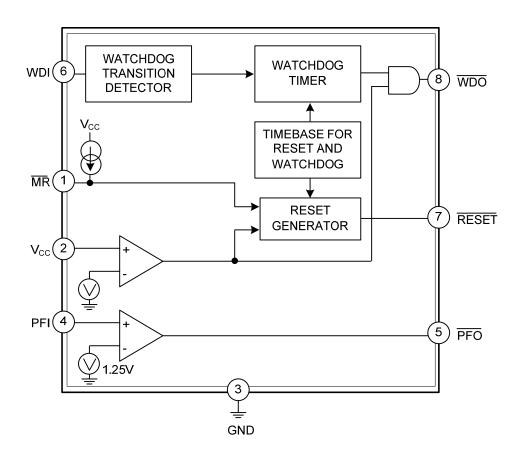

## ■ BLOCK DIAGRAM

## ■ ABSOLUTE MAXIMUM RATING

| PARAMETER                              | SYMBOL           | RATINGS                     | UNIT |

|----------------------------------------|------------------|-----------------------------|------|

| Terminal Voltage (with respect to GND) | V <sub>CC</sub>  | -0.3 ~ 6.0                  | V    |

| All Other Inputs                       | $V_{IN}$         | $-0.3 \sim (V_{CC} + 0.3V)$ | V    |

| Input Current, V <sub>CC</sub> , GND   | Icc              | 20                          | mA   |

| Output Current, (all outputs)          | I <sub>OUT</sub> | 20                          | mA   |

| Junction Temperature                   | $T_J$            | +150                        | °C   |

| Operating Temperature Range            | T <sub>OPR</sub> | -40 ~ <b>+</b> 85           | °C   |

| Storage Temperature                    | T <sub>STG</sub> | -65 ~ +150                  | °C   |

Note: Absolute maximum ratings are those values beyond which the device could be permanently damaged. Absolute maximum ratings are stress ratings only and functional device operation is not implied.

## ■ **ELECTRICAL CHARACTERISTICS** (T<sub>A</sub>=25°C, unless otherwise specified)

| PARAMETER               |                   | SYMBOL          | TEST CONDITIONS                                | MIN                  | TYP  | MAX  | UNIT |

|-------------------------|-------------------|-----------------|------------------------------------------------|----------------------|------|------|------|

| Operating Voltage Range |                   | Vcc             |                                                | 1.0                  |      | 5.5  | V    |

| Supply Current          |                   | ISUPPLY         |                                                |                      | 50   | 250  | μΑ   |

| Reset Threshold         | UWD706-A          | V <sub>RT</sub> |                                                | 2.56                 | 2.63 | 2.69 | V    |

|                         | UWD706-B          |                 |                                                | 2.83                 | 2.93 | 2.99 | V    |

|                         | UWD706-C          |                 |                                                | 3.01                 | 3.08 | 3.15 | V    |

|                         | UWD706-D          |                 |                                                | 3.91                 | 4.0  | 4.08 | V    |

|                         | UWD706-H          |                 |                                                | 4.25                 | 4.4  | 4.5  | V    |

|                         | UWD706-G          |                 |                                                | 4.5                  | 4.65 | 4.75 | V    |

| Reset Threshold Hyste   | resis             |                 |                                                |                      | 60   |      | mV   |

| Reset Pulse Width       |                   | t <sub>RS</sub> |                                                | 110                  | 200  | 300  | ms   |

|                         |                   |                 | I <sub>SOURCE</sub> = 800µA                    | V <sub>CC</sub> -1.5 |      |      | V    |

| RESET Output Voltage    | Э                 |                 | I <sub>sink</sub> =3.2mA                       |                      |      | 0.4  | V    |

|                         |                   |                 | V <sub>CC</sub> =1V, I <sub>sink</sub> =50μA   |                      |      | 0.3  | V    |

| Watchdog Timeout Per    | iod               | t <sub>WD</sub> |                                                | 8.0                  | 1.6  | 2.4  | sec  |

| WDI Pulse Width         |                   | t <sub>WP</sub> | $V_{IL}$ =0.4 $V$ , $V_{IH}$ = $V_{CC}$        |                      | 70   |      | ns   |

|                         | Low               |                 | V <sub>CC</sub> =5V                            |                      |      | 0.5  | V    |

| WDI Input Threshold     | High              |                 | V <sub>CC</sub> =5V                            | 3.5                  |      |      | V    |

| WDI Input Threshold     | Low               |                 | V <sub>RST(MAX)</sub> < V <sub>CC</sub> < 3.6V |                      |      | 0.5  | V    |

|                         | High              |                 | V <sub>RST(MAX)</sub> < V <sub>CC</sub> < 3.6V | 0.7×V <sub>CC</sub>  |      |      | V    |

| WDU 10 1                |                   |                 | WDI=V <sub>CC</sub>                            |                      | 50   | 150  | μΑ   |

| WDI Input Current       | WDI Input Current |                 | WDI=0V                                         | -150                 | -50  |      | μΑ   |

| WDO Output Voltage      |                   |                 | I <sub>SOURCE</sub> =800µA                     | V <sub>CC</sub> -1.5 |      |      | V    |

|                         |                   |                 | I <sub>sink</sub> =1.2mA                       |                      |      | 0.4  | V    |

| MR Pull-Up Current      |                   |                 | MR = 0V                                        |                      | 500  |      | μA   |

| MR Pulse Width          |                   | t <sub>MR</sub> |                                                | 250                  |      |      | ns   |

|                         | Low               |                 | T - 125°C                                      |                      |      | 0.8  | V    |

| MR Input Threshold      | High              |                 | T <sub>A</sub> = +25°C                         | 2                    |      |      | V    |

| MR to Reset Out Delay   |                   | t <sub>MD</sub> |                                                |                      |      | 350  | ns   |

| PFI Input Threshold     |                   |                 |                                                | 1.1                  | 1.25 | 1.3  | V    |

| PFI Input Current       |                   |                 | V <sub>CC</sub> = 5V                           |                      | 0.2  |      | nA   |

| PFO Output Voltage      |                   |                 | I <sub>SOURCE</sub> = 800μA                    | V <sub>CC</sub> -1.5 |      |      | V    |

|                         |                   |                 | I <sub>sink</sub> =3.2mA                       |                      |      | 0.4  | V    |

**UWD706**

#### **■ APPLICATION NOTES**

## Ensuring a Valid RESET Output Down to Vcc=0V

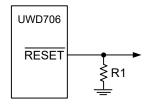

When  $V_{CC}$  falls below 1V, the **UWD706**  $\overline{RESET}$  output no longer sinks current—it becomes an open circuit. High-impedance CMOS logic inputs can drift to undetermined voltages if left undriven. If a pull-down resistor is added to the  $\overline{RESET}$  pin as shown in Figure 1, any stray charge or leakage currents will be drained to ground, holding  $\overline{RESET}$  low. Resistor value (R1) is not critical. It should be about  $100k\Omega$ , large enough not to load  $\overline{RESET}$  and small enough to pull  $\overline{RESET}$  to ground.

Figure 1. RESET Valid to Ground Circuit

#### Monitoring Voltages Other Than the Unregulated DC Input

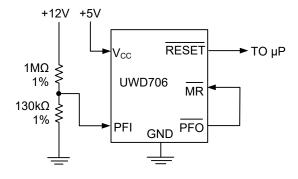

Monitor voltages other than the unregulated DC by connecting a voltage divider to PFI and adjusting the ratio appropriately. If required, add hysteresis by connecting a resistor (with a value approximately 10 times the sum of the two resistors in the potential divider network) between PFI and  $\overline{\text{PFO}}$ . A capacitor between PFI and GND will reduce the power-fail circuit's sensitivity to high-frequency noise on the line being monitored.  $\overline{\text{RESET}}$  can be asserted on other voltages in addition to the +5V V<sub>CC</sub> line. Connect  $\overline{\text{PFO}}$  to MR to initiate a  $\overline{\text{RESET}}$  pulse when PFI drops below 1.25V. Figure 2 shows the **UWD706** configured to assert  $\overline{\text{RESET}}$  when the +5V supply falls below the reset threshold, or when the +12V supply falls below approximately 11V.

Figure 2.Monitoring Both +5V and +12V

UWD706 cmos ic

### ■ APPLICATION NOTES (Cont.)

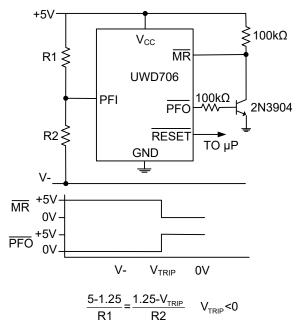

## **Monitoring a Negative Voltage**

The power-fail comparator can also monitor a negative supply rail (Figure 3). When the negative rail is good (a negative voltage of large magnitude),  $\overline{PFO}$  is low, and when the negative rail is degraded (a negative voltage of lesser magnitude),  $\overline{PFO}$  is high. By adding the resistors and transistor as shown, a high  $\overline{PFO}$  triggers reset. As long as  $\overline{PFO}$  remains high, the **UWD706** will keep reset asserted ( $\overline{RESET}$  = low,  $\overline{RESET}$  = high). Note that this circuit's accuracy depends on the PFI threshold tolerance, the V<sub>CC</sub> line, and the resistors.

Figure 3. Monitoring a Negative Voltage

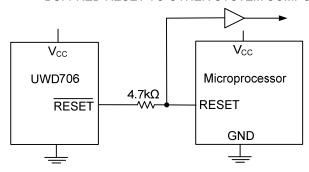

## Interfacing to µPs with Bidirectional Reset Pins

$\mu$ Ps with bidirectional reset pins can contend with the **UWD706** RESET output. If, for example, the RESET output is driven high and the Microprocessor wants to pull it low, indeterminate logic levels may result. To correct this, connect a 4.7kΩ resistor between the RESET output and the  $\mu$ P reset I/O, as in Figure 4. Buffer the RESET output to other system components.

#### BUFFRED RESET TO OTHER SYSTEM COMPONENTS

Figure 4. Interfacing to Microprocessors with Bidirectional Reset I/O

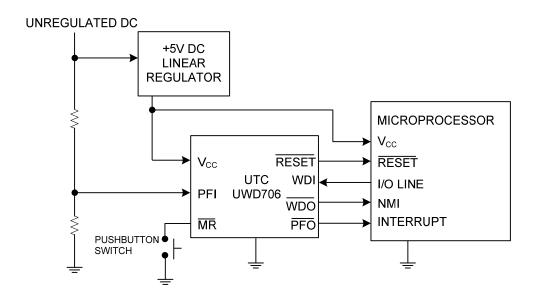

## ■ TYPICAL APPLICATION CIRCUIT

## ■ TYPICAL CHARACTERISTICS

Power-Fail Comparator Deassertion Response Time

PFI

PFI

PFO

PFO

OV

OV

OV

DESCRIPTION OF THE PROPERTY O

UTC assumes no responsibility for equipment failures that result from using products at values that exceed, even momentarily, rated values (such as maximum ratings, operating condition ranges, or other parameters) listed in products specifications of any and all UTC products described or contained herein. UTC products are not designed for use in life support appliances, devices or systems where malfunction of these products can be reasonably expected to result in personal injury. Reproduction in whole or in part is prohibited without the prior written consent of the copyright owner. UTC reserves the right to make changes to information published in this document, including without limitation specifications and product descriptions, at any time and without notice. This document supersedes and replaces all information supplied prior to the publication hereof.